Why Choose Us!

Best DFT Training Institute in Bengaluru | DFT Training Course

Course Description

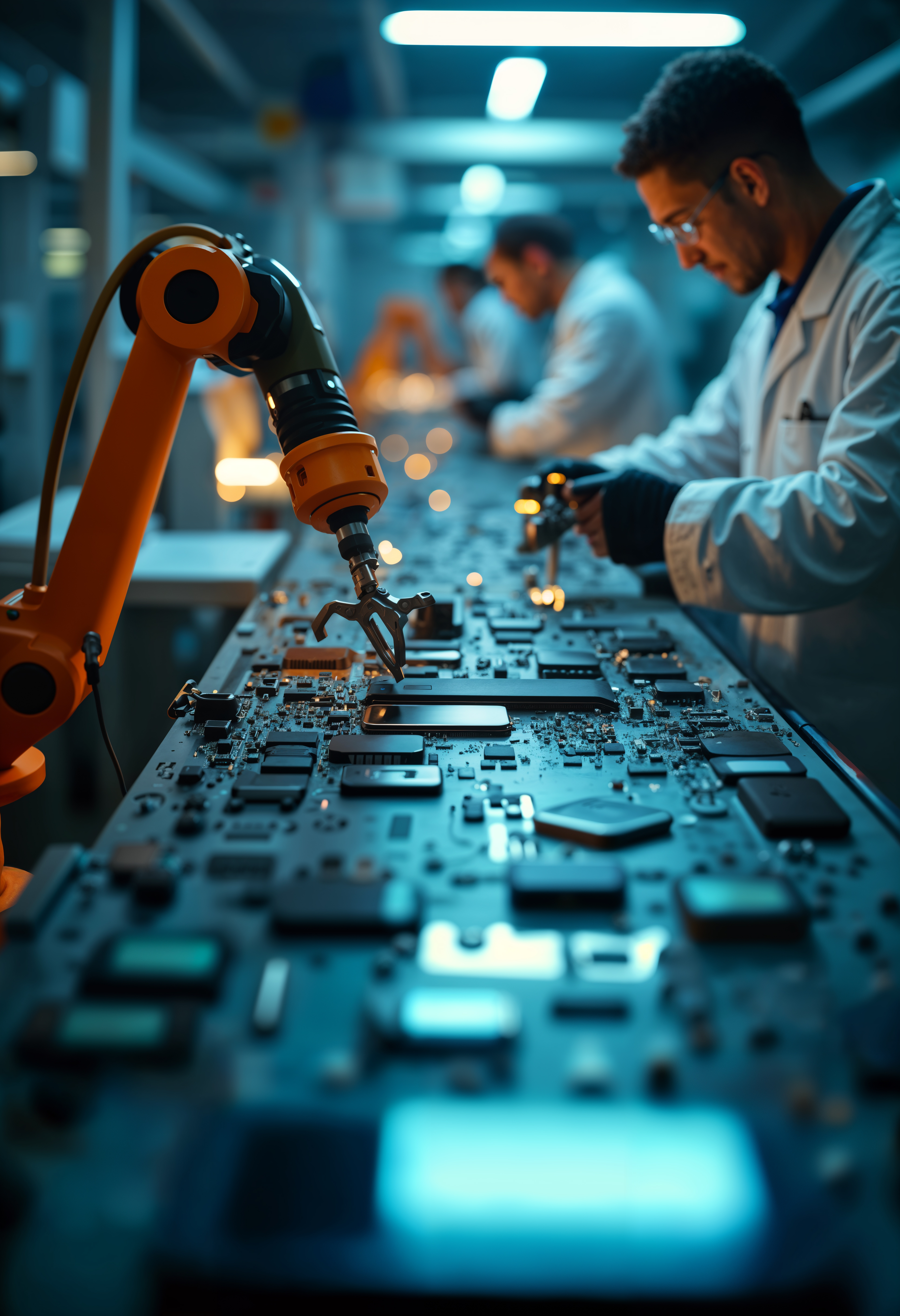

Design for Testability (DFT) is a critical specialization within the SoC design cycle, aimed at ensuring the detection of manufacturing defects in semiconductor

designs. As chip size and complexity continue to grow due to advancements

in manufacturing technology, DFT has become an essential discipline in the VLSI industry.

DFT Engineers are responsible for introducing specialized test structures to enhance the testability of logic, memory, and interconnects, making it easier to identify faults post-manufacture.

Our DFT Training Course is crafted to align with current industry standards, featuring hands-on projects in:

✅ SCAN Insertion

✅ ATPG (Automatic Test Pattern Generation)

✅ JTAG (Boundary Scan Testing)

✅ FMBIST (Memory Built-In Self-Test)

Industry-Standard VLSI & DFT Training

Eligibility

🎓 B.E / B.Tech in ECE / EEE

🎓 M.E / M.Tech / M.S in VLSI / Embedded Systems / Digital Electronics

Course Highlights

🔧 Hands-on exposure to the entire Design for test flow using industry-standard EDA tools

📚 In-depth understanding of methodologies and technologies used in today’s semiconductor industry

💻 24×7 Lab Access, with lab handouts and comprehensive course materials

🔨 End-to-End Project Execution, from RTL to GDSII, under the mentorship of industry experts with 12+ years of experience

🧑💼 Soft Skills Development & Placement-Oriented Training, with 100% placement assistance

Fully Licensed

Online Tracking

Afordable Fee

Best Trainers