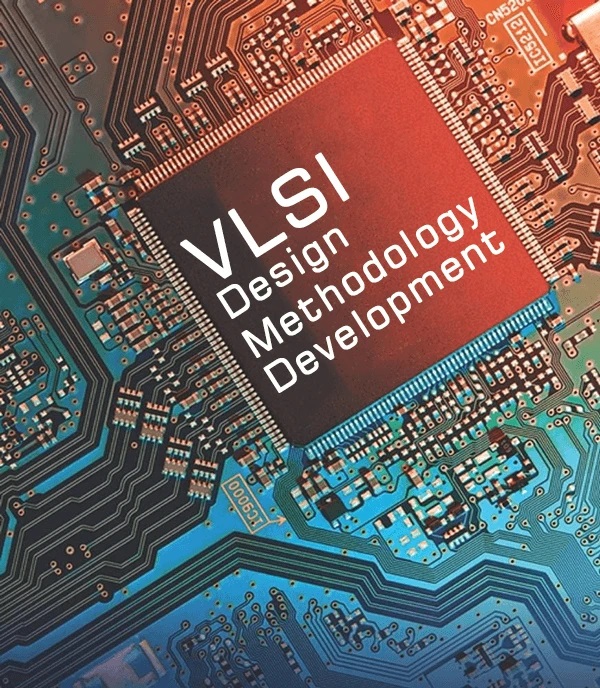

Master VLSI Design with Industry Experts! Get hands-on training and build a strong foundation in chip design

Learn More Our Courses

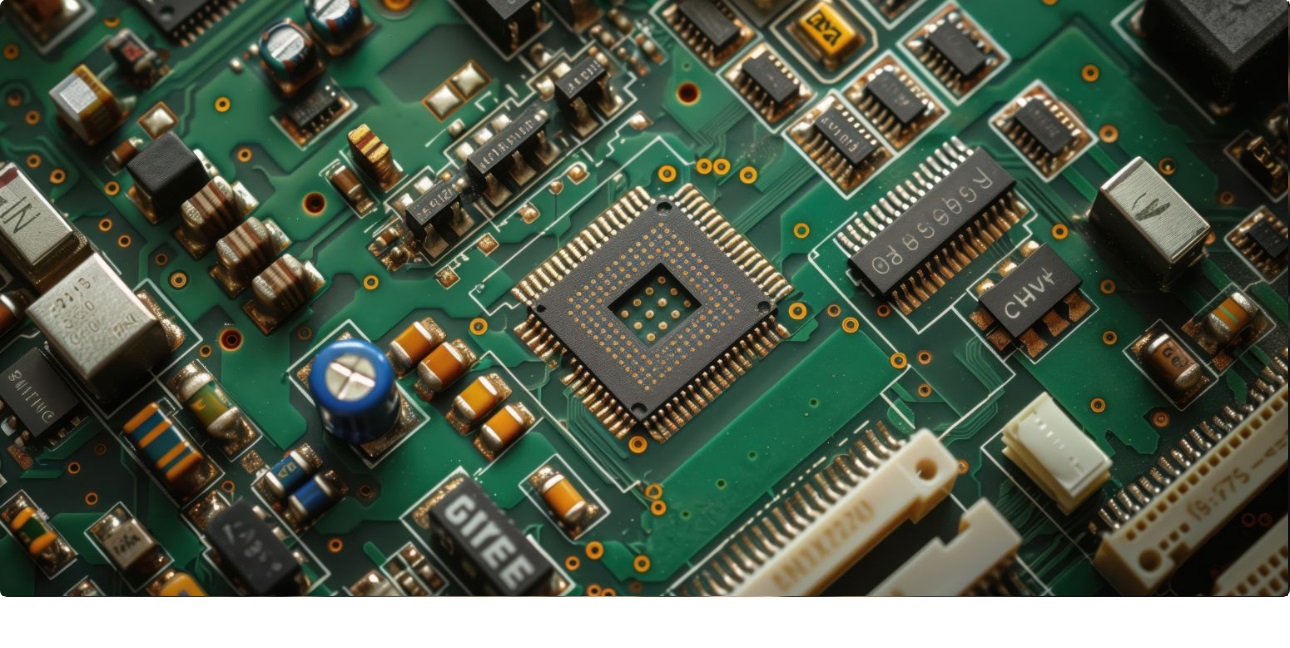

We are a leading provider of VLSI training, dedicated to equipping aspiring engineers with industry-relevant skills and hands-on experience in chip design, ASIC, FPGA, SoC, and semiconductor technologies. Our expert-led courses are designed to bridge the gap between academia and industry, preparing students for high-demand careers in VLSI design and verification.

With a strong focus on practical learning, real-world projects, and placement assistance, we ensure our trainees are job-ready and excel in the fast-growing semiconductor industry. Join us and take the first step toward a successful career in VLSI!

A Physical Design Engineer is responsible for transforming RTL code into a manufacturable layout by handling floorplanning, placement, routing, timing closure, and power optimization in the VLSI design flow.

DFT (Design for Testability) is a VLSI methodology that integrates test structures into a chip to enable efficient fault detection and manufacturing testing.

Design Verification ensures that a VLSI chip's design functions correctly by using simulation, formal verification, and debugging techniques to detect and fix errors before fabrication.

✅ Expert-Led Training – Learn from industry professionals with real-world experience.

✅ Comprehensive Curriculum – Covering ASIC, FPGA, Physical Design, DFT, and more.

✅ Hands-On Projects – Gain practical skills with industry-standard tools.

✅ Placement Assistance – Get job-ready with interview prep and networking opportunities.

✅ Latest EDA Tools – Work with cutting-edge semiconductor design software.

Dolores sed duo clita tempor justo dolor et stet lorem kasd labore dolore lorem ipsum. At lorem lorem magna ut et, nonumy et labore et tempor diam tempor erat.

Dolores sed duo clita tempor justo dolor et stet lorem kasd labore dolore lorem ipsum. At lorem lorem magna ut et, nonumy et labore et tempor diam tempor erat.

Dolores sed duo clita tempor justo dolor et stet lorem kasd labore dolore lorem ipsum. At lorem lorem magna ut et, nonumy et labore et tempor diam tempor erat.